BM80

Member

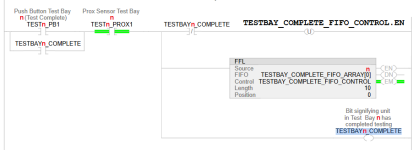

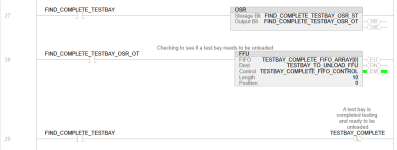

I have a project that is loading pallets into 10 test bays and then unloading them when the test is complete. I am using an array to store which test bays have completed testing and using an FFL command to store them in the array, so they are unloaded in a FIFO order. I am having an issue with the FFL consistently loading a completed test bay's number. Out of 100 times 6 or so may not load into the array. There is a prox sensor in each test bay that senses the pallet and when the test is complete the operator presses a push button at the test bay. If the button is pressed and the prox sensor senses a pallet then a test complete tag is latched for that test bay. An OSR of the this latched tag is used to MOV a test bay number into a tag which is then used as the source for the FFL command to load into the array. The test complete tag is getting latched, so I know that part is working correctly. I can't seem to figure out why this is randomly not working. Attached is the routine if anyone cares to look at it. The part of the routine starts at rung 10.